Pipeline işlemci mimarisine genel olarak değinmek istiyorum. İşlemcinin paralel olarak işlem yapabilmesini sağlayan tekniktir. İşlemcinin komutu alması, çözmesi ve işleme sokması gibi aşamalar düşünüldüğünde, bir komutun işleme alınmasıyla işlemin tamamlanıp farklı bir komuta geçilene kadarki sürede sadece o komutla ilgilendiğini görürüz. Farklı bölümler kendi işlerini yaptıktan sonra diğer bölümlerin de işlerini yapmasını beklemektedir. Bu da çok fazla zaman kaybına neden olmaktadır. Bu sebeple Pipeline Mimarisi düşünülmüştür. Bu mimariyi bir örnekle açıklayacak olursak, günümüzde fabrikalarda üretim aşamasında çokça kullanılan üretim bantlarını göz önüne alalım. Bu bantlar hareket ettikçe malzemeler bekleyen işçilerin önüne gelir, her işçi kendi yapacağı işi kısa sürede yapar ve bir sonraki ürünün önüne gelmesini bekler. Bu yapıyla zamandan büyük oranda tasarruf edilerek üretimde verimlilik sağlanmış olur.

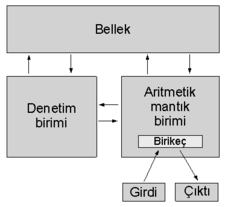

Üretim bandındaki yapıyı komutların işlenmesine benzetelim. Diyelim komutu fetch etmek t1 süre, çözmek t2 süre, icra etmek ise t3 süre alsın. Böylelikle t = t1 + t2 + t3 sürede sadece bir işlem yapılacaktır. Pipeline mimarisine uyarladığımızda ise t1 süresinde komut fetch edildikten sonra komutun çözülmesinde geçildiği andan sonraki komut fetch edilmeye başlanacaktır. Böylelikle t1 ,t2 ve t3 sürelerinin eşit olduğunu farzettiğimiz taktirde t1 = t2 = t3 = t olur ve zamandan üç kat tasarruf etmiş oluruz. Bu değerlerin eşit olmadığı taktirde ise bu üç değerin birbirine yakın olması en verimli sonucu verecektir. Aradaki farkın açılmasında ise bir komutun işlenme süresi artacaktır. Modern bilgisayarlarda bu işlemlerin her biri bir clock palsinde gerçekleşmektedir. Yani Pipeline’sız olarak 3 clock palsinde bir işlem yapılırken, Pipeline Mimarisi ile her clockta bir işlem gerçekleşmektedir (başlangıçtan üç clock palsi sonrasından itibaren). Yukarıda sadece üç aşamadan bahsettim ama bu aşamalar fetch, decode, execute, memory ve write back olarak beşe kadar çıkabilmektedir.

Avantajları:

- Zaman tasarrufu sayesinde işlem hacmi artar.

- ALU tasarımı daha hızlıdır.

Dezavantajları :

- Dallanma işlemleri en büyük problemleridir. Dallanılacak yerin önceden bilinememesi performansı düşürür. Atlama komutu çalışmadan sonraki komutun ne olacağı bilinemez.

- ALU tasarımı daha karmaşıktır.

- Pipelined bir sistemin yönerge gecikmesi(latency), pipelined olmayana göre biraz daha fazladır.

- Bu da sisteme ekstra flip-floplar eklenmesinden kaynaklanır.

- Pipelined bir sistemin işlemci performansını ölçmek daha zordur ve performans daha değişkendir.